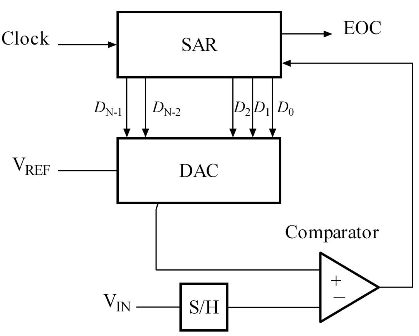

これは、SAR ADCのブロック図です(図の出典:wikpedia.orgのSAR ADC)。DACの出力と、入力電圧VINをコンパレータで比較するように構成されています。両者の大小関係はコンパレータで分かりますから、ロジック回路SARはコンパレータの出力を見て、Vinに最も近くなるように、DACをカチカチと動かします。S/Hは、サンプルホールドのことで、VINの電圧を記憶して、変換の最中保持し続けるという意味です。できるだけ比較回数を少なくして、効率よく解を求めるためには、2分検索が適しているため、ほとんどのSAR ADCは、2分検索するように作られています。

さて、実際の回路はどうなっているのでしょうか?より具体的に見てゆきたいと思います。

この絵は、USP 4129863からとってきました。

MOS集積回路では、トランジスタをスイッチとして使えますから、スイッチが多用されています。容量素子も、原理的には2枚の電極があって、その間に絶縁物があれば良いわけですから、各種方法で作成することが可能です。VINは入力信号の電圧、VREFは基準電圧です。

容量はそれぞれC, C/2, C/4, C/8, C/8のように二進的に重み付けされていて、DACになっています。この回路では、容量はDACとして動作するとともに、S/Hの役割も果たします。スイッチの設定によっては、VINを容量のボトムプレート(図の下側のノード)へ接続できるようになっていることに注目してください。

変換の冒頭では、サンプリングするために、S1を接続して、S2~S6を”2″に接続して、S7をVINに接続します。そうしますと、Vxは0Vに、容量の下側ノードはVINにされます。その次に、サンプリングを終えてホールドするためにS1を開放します。

上記操作の後、S7をVREFに接続し、コンパレータの比較結果を見ながらS2~S6を操作して、Vxが0Vの近づくようにします。そうすると、最終的なS2~S6の設定値が、A/D変換の結果に相当します。直感的に理解するために、VINの電圧が0Vだった場合と、VINの電圧がVREFだった場合の2とおりを考えてみますと、

VIN=0Vがサンプリングされた時、Vxの電位が0Vになるためには、S2~S6は”1″側に接続されなくてはならない

VIN=VREFがサンプリングされた時、Vxの電位が0Vになるためには、S2~S6は”2″側に接続されなくてはならない

ことが分かります。

このように、サンプリングされたVINの電位によって、Vx=0VとなるS2~S6の設定が変化しますので、この値をデジタルコードとして出力するわけです。

DACに必要な容量を使ってS/Hの機能も実現できて、大変簡単な回路済むことがお分かり頂けると思います。この回路の動作は、信号電圧に応じた電荷をサンプリングして、バイナリで加重された容量に分配する動作と見ることができるため、”Charge Redistribution(電荷再分配)”方式と呼ばれています。現在入手可能なSAR ADCのほとんどは、多少の変形があるものの、以上のようなメカニズムで動作しています。

先に示した特許が1977年にUCBのP. R. Grayらが書いたものなので、30年以上前に考えられたものです。

以上、簡単書いてみました。より詳細な解析は、時間があったら書こうと思います。

関連記事:

コメント